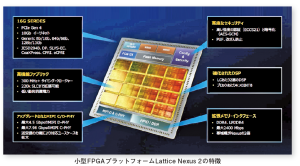

ラティスセミコンダクターは,ロジック数65K〜220KのプラットフォームLattice Nexus 2を発表した.同社の既存のプラットフォームはロジック数が最大100 KのNexusと最小300KのAvantで,その間の空いたロジック数の製品を補完する.

競合製品に比べて消費電力は1/3,エッジ・センサのモニタリングにおけるエネルギー効率は最大10倍,コンフィグレーションの時間は10倍速いとする.

マルチプロトコル16G SERDESとPCIe Gen 4コントローラ,LPDDR4メモリ・インターフェースをサポート.MIPID&C-PHYは最大7.98Gbps.セキュリティは256ビットのAES-GCMとSHA3-512により,暗号化ベンチマークFIPS140-3のレベル2規格にも準拠する.

製造プロセスはTSMCの16nm Fin FET.

同プラットフォームの1製品目は汎用FPGAのCertus-N2で65K/100K/160K/220Kの4製品が用意されている.設計ツールはLattice PropelとLattice Radiant.汎用に続き,ビデオ・コネクティビティ用 CrossLink や不揮発性メモリ内蔵のMachも発売予定.

ライター:編集部